数据库

嵌入式硬件

编码

html

机器视觉

测试用例

云idea

知识蒸馏

jenkins

寒武纪笔试

免责声明

端口号概念

山区监视场景建模

新媒体运营

BH1750

应力强度因子

知识计算

安卓app

swiftu

parser

AXI

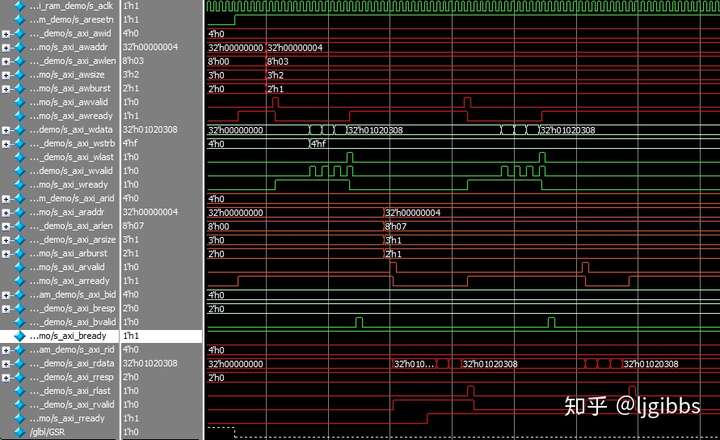

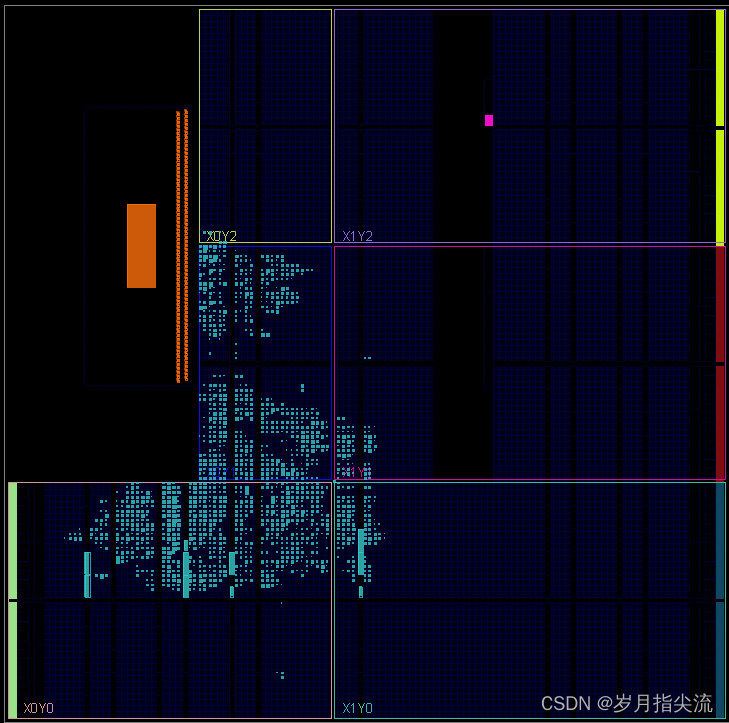

2024/4/12 0:22:19深入 AXI4总线 (四):RAM 读取实战

光说不练,云玩家。这篇文章中我们就通过访问一个 AXI4 接口的 RAM 的实际操作,加深我们对 AXI4 总线的理解。

我们的实验平台是 ISE 14.7 以及 modelsim 10.2, RAM 的 ip 使用 ISE 的 block memory generator 生成,Intel 方面的工具和 ip 我…

深入 AXI4 总线(三)突发传输机制

本文参考AMBA AXI and ACE Protocol Specification 来写 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。本篇文章我们将讨论有关…

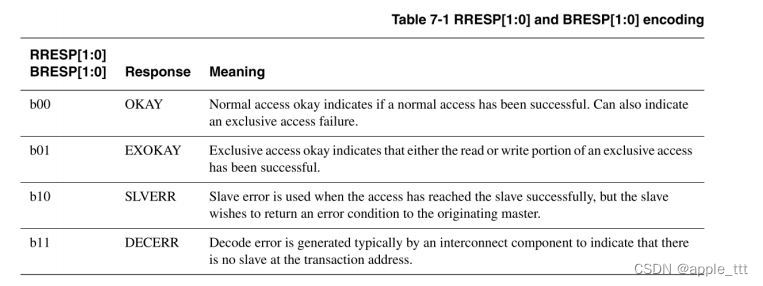

深入浅出AXI协议(5)——数据读写结构读写响应结构

目录 一、前言

二、写选通(Write strobes)

三、窄传输(Narrow transfers)

1、示例1

2、示例2

四、字节不变性(Byte invariance)

五、未对齐的传输(Unaligned transfers)

六…

AXI 总线协议学习笔记(3)

引言

上篇文章主要介绍了 AMBA以及AXI协议的基本内容,本文接续前文,继续介绍AXI协议的 原子访问、传输行为和事务顺序等。

AXI 总线协议学习笔记(2)https://blog.csdn.net/qq_43045275/article/details/128824643 原子访问

原子…

AXI 总线协议学习笔记(2)

引言

从本文开始,正式系统性学学习AXI总线。

如何获取官方协议标准?

第一步:登陆官网:armDeveloper

第二步:登录,无账号需要注册

第三步:点击文档 第四步: 第五步:浏…

AXI 总线基本概念 - 如何理解outstanding传输

在AXI4的总线规范中提到AXI4的总线特性之一: Support for issuing multiple outstanding addresses.

从字面理解,outstanding表示正在进行中的,未完成的意思,形象地说就是“在路上”。

简单讲,如果没有outstandin…

深入浅出AXI协议(4)——猝发传输

一、前言 在之前的文章中,我们着重介绍了关于AXI4的握手协议它可以使得传输的双方都可以自如地控制传输的速率,我们主要介绍了握手协议出现的3种可能情况。然后对于AXI4交易通信的握手信号的关系做出了介绍:(1)在AXI4互…

深入 AXI4 总线(一)握手机制

VALID/READY 握手机制

AXI 总线共有 5 个独立的通道,分别为写地址,写数据,写回应,读地址,读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制…

AXI总线(top)

AXI总线是一种基于burst的传输总线,适合用在high-bandwidth和low-latency的场景,大致分为5个通道:

read addressread datawrite addresswrite datawrite response

AXI总线支持:

1)unaligned data transfer,包括SIZE的…

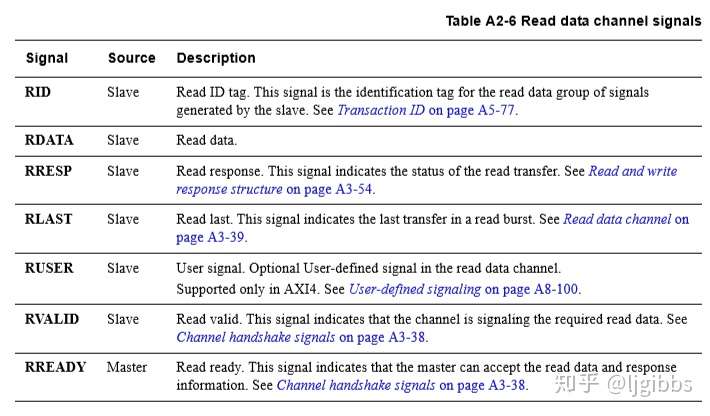

深入浅出AXI协议(2)——通道及信号

一、前言 在之前的文章中,我们主要介绍了什么是AXI协议,AXI协议的特点与优点,然后对于AXI协议非常重要的五通道结构进行了介绍,了解了5个通道各自的作用。本文我们继续AXI协议的学习,我们将讨论5个通道的具体内容和相对…

深入浅出AXI4协议(1)——概述

写在前面 从这篇文章开始,我们将正式进入AXI4协议的学习,在xilinx系列的FPGA中,AXI4协议的使用是非常广泛的,很多的IP核都会支持AXI接口,而如果使用的是zynq系列,那AXI协议的学习更是重中之重。但是作为一款…

【ZYNQ】AXI4总线接口协议学习

建议翻看着底部的参考文档资料和本文一起辅助阅读 本文带你详细的了解AXI总线协议,并且基于官方手册,能够提高你的手册阅读能力。 什么是AXI

AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提…

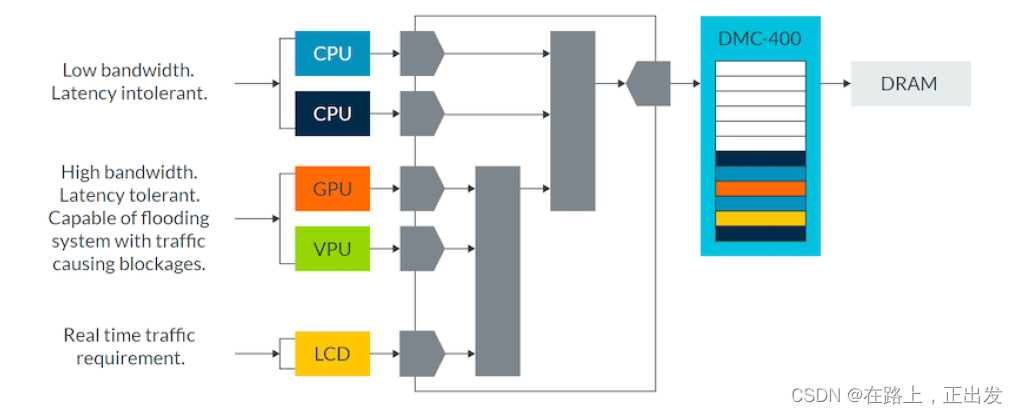

虹科AXI性能监视器 | 高集成度SoC开发调试

APM,AXI Performance Monitor,AXI性能监视器。AXI是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问࿰…

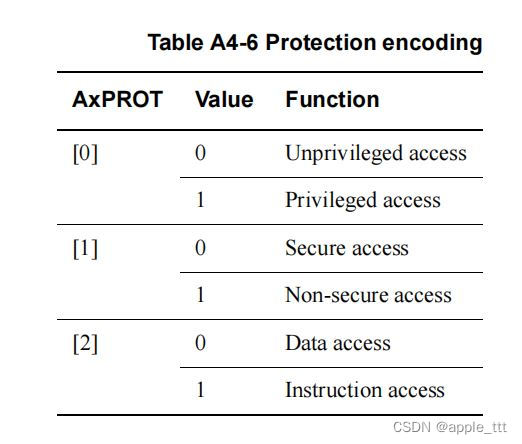

深入浅出AXI协议(6)——传输属性

一、前言 在之前的文章中,我们介绍的主要内容是AXI协议的数据读写结构和读写响应结构,主要讲述了当遇到各种特殊情况时,AXI如何完成数据的读写操作,最后介绍了读写响应的4种类型。 在本文中,我们将介绍AXI协议的传输属性。

二、传…

AXI-Lite 学习笔记

AXI-Lite 学习笔记 参考 FPGA:AXI_Lite总线基础2-1]、第二节 AXI总线介绍、ZYNQ PL与PS交互专题_哔哩哔哩_bilibili AXI-Lite总线系列1 - 基础知识_哔哩哔哩_bilibili AXI4 介绍

AXI4 是ARM公司提出的一种片内总线,描述了主从设备之间的数据传输方式。主…

System Generator学习——使用 AXI 接口和 IP 集成器

文章目录 前言一、目标二、步骤1、检查 AXI 接口2、使用 System Generator IP 创建一个 Vivado 项目3、创建 IP 集成设计(IPI)4、实现设计 总结 前言

在本节中,将学习如何使用 System Generator 实现 AXI 接口。将以 IP 目录格式保存设计&am…

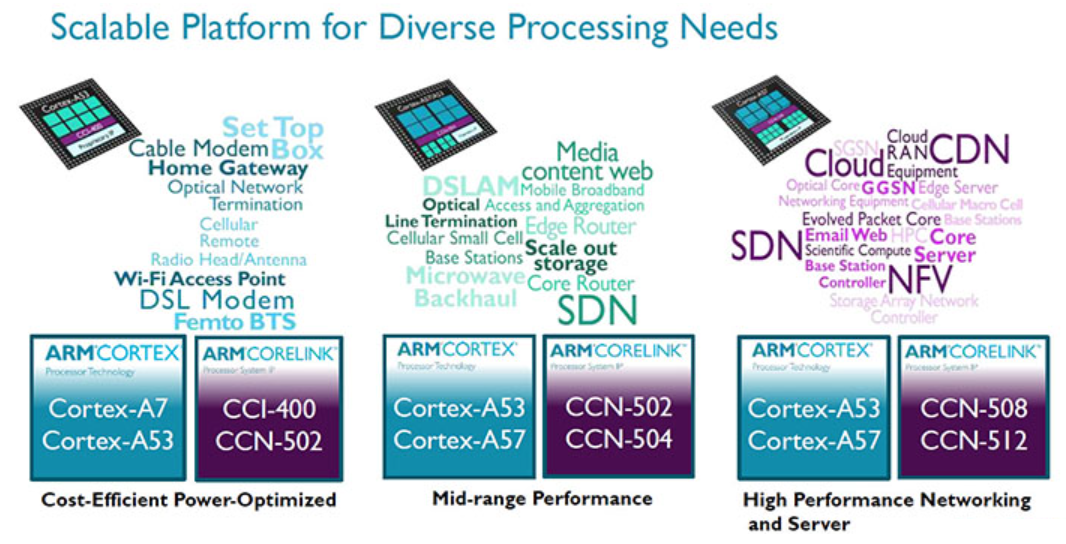

ARM CoreLink CCN 互连总线介绍

NIC NOC CCI CMN CNN NI cmn-700 nic-700 ni-700 MLGB这都是啥玩意? 后期博文或视频将会更新这一系列。今天先温习一下CNN的概念,这是来自2014年的文章,然后稍微整理总结一番。 以下是正文… 现代主流和优质 ARM 片上系统 (SoC) 产品使用 CoreLink 缓存一致性网络 (CCN) 504…

【Altera】平台设计器互连会回压 AXI 接口怎么办

说明 实现 AXI 接口的所有组件都具有发行或接受能力设置。每当互连检测到管理器(主管理器)发出的事务多于管理器的发行容量设置时,互连将通过断言 AxREADY 向管理器背压。每当互连检测到从属(从站)接收的事务多于从属的…

AMBA_AXI Protocol Introduction

AXI Protocol Introduction

1. AXI协议特性

2. AXI协议关键特性

3. AXI 协议结构

4. Interface and interconnect

5. Register slicesAMBA AXI协议为主机与从机组件之间的通信提供高性能,高频系统设计 1. AXI协议特性

适用于高带宽,低延迟设计不使用复…

AMBA总线协议AHB、APB、AXI对比分析

一、AMBA概述 AMBA (Advanced Microcontroller Bus Architecture) 高级处理器总线架构 AHB (Advanced High-performance Bus) 高级高性能总线 ASB (Advanced System Bus) 高级系统总线 APB (Advanced Peripheral Bus) 高级外围总线 AXI (Advanced eXtensible Interface) 高…

深入 AXI4 总线(二)架构

五个独立通道

AXI4 总线的一大特征是它有 5 个独立的传输通道,这些通道都只支持单向传输。作为类比,SPI 总线有 2 条传输通道:MISO, MOSI。SPI 输入输出的数据,大路朝天,各走一条;而作为对比&a…

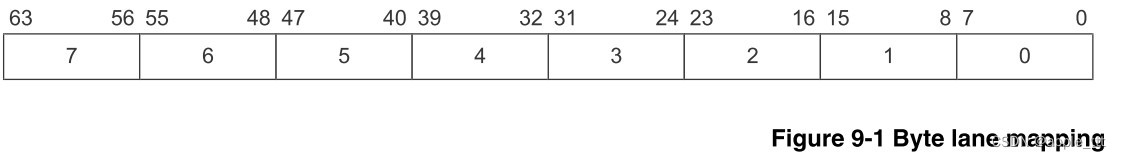

AMBA_AXI Protocol_Burst Address

AXI Protocol_Burst Address

Burst Address(Bus地址)

1. Burst 地址

2. Byte lane本节提供确定突发内传输的地址和字节选通(byte lane)的方法。方程使用以下变量:

Start_Address:由主机发出的起始地址。Number_Byte…

【ARM AMBA AXI 入门 2 - AXI协议中的BURST】

文章目录 1.1 突发传输简介1.1.1 AXI4 突发传输控制信号1.1.1.1 AxLEN 突发传输长度1.1.1.2 AxSIZE 突发传输宽度1.1.1.3 AxBURST 突发传输类型 1.1.2 AXI 传输实例 1.1 突发传输简介

在地址总线上进行一次地址传输后,进行多次数据传输( data transfer)…

AMBA-AXI(三)exclusive传输

💡Note:本文是根据AXI协议IHI0022F_b_amba_axi_protocol_spec.pdf(issue F)整理的。主要是分享AXI3.0和4.0部分。如果内容有问题请大家在评论区中指出,有补充或者疑问也可以发在评论区,互相学习ὤ…

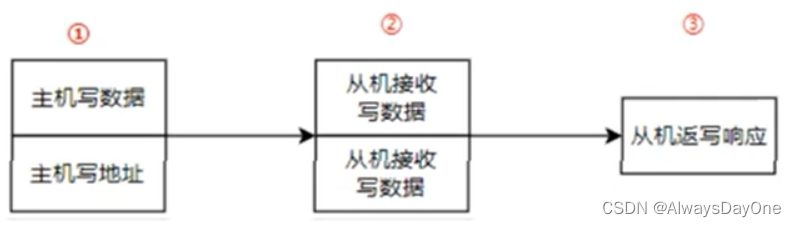

AMBA_AXI Protocol_基本读写事务

基本读写事务

1. 握手的过程

2. 信道信令要求

3. 通道之间的关系1. 握手的过程

当地址、数据或控制信息可用时,源端(source)产生VALID信号。终端(destination)生成READY信号,表示它可以接受该信息。传输只…

解读AMBA总线协议,一文稿定ACECHIAXI

无论你是IC设计工程师、验证工程师、FPGA工程师、还是微电子相关专业的学生,对于AMBA总线一定不陌生。 随着技术迭代的发展、基于各种复用IP的SoC芯片场景被高度使用,越来越多的人开始和总线互联打交道。 你肯定听说过AMBA、AHB、APB、AXI、ACE

一、A…

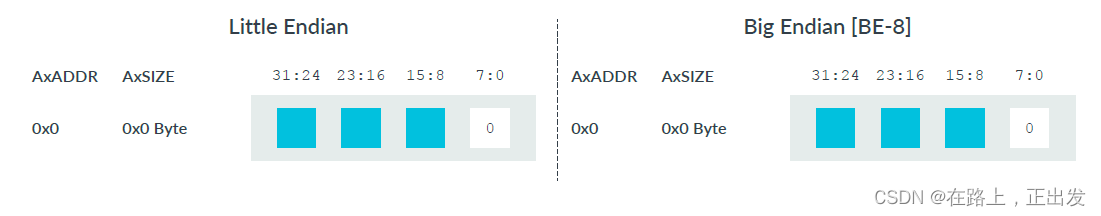

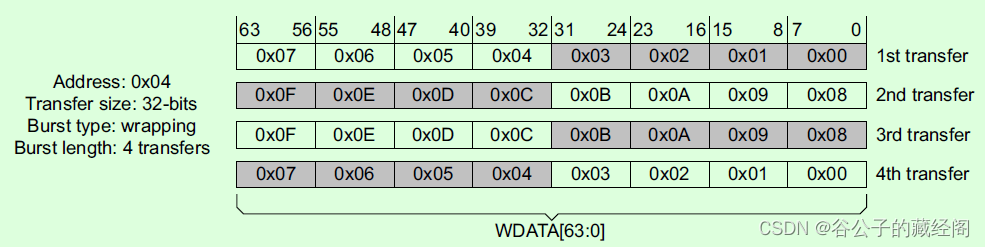

AXI write data在Write data channel的排布

前几天帮一位同事分析了下write data在AXI write data channel上排布,想想还是记录一下,方便日后复习。我们先来看一张wdata排布图,灰色单元表示该Byte没有被传输。 第一次看这张图的时候,是否有感觉疑惑:

address为0…

解读AXI协议,做一个不被AXI折磨的芯片设计工程师

作为一名IC芯片工程师,我深知AXI(Advanced eXtensible Interface)协议给我们带来的痛苦和挑战。在过去的项目中,我经历了与AXI协议相关的许多问题和困惑,但我也学到了一些宝贵的经验。现在,我想分享一些关于…

【ARM AMBA AXI 入门 6 - AXI3 协议中的锁定访问之AxLOCK信号】

文章目录 1.1 Locked accesses 1.1 Locked accesses

当主机使用 AxLOCK 信号来指示事务是锁定的事务时,互连(Interconnect)必须确保只有该主机可以访问目标从属区域,直到来自同一主机的未锁定事务完成。互连中的仲裁器(arbiter)必须执行此限制。

在主机…